## 7-Level Semi Cross Switched Multilevel Inverter Fed Induction Motor Drive

Srinivas Rao Janiga<sup>1,\*</sup>, and Suresh Kumar Tummala<sup>2</sup>

<sup>1</sup>Assistant Professor, EEE Department, Anurag Engineering College, Kodad, India

<sup>2</sup>Professor, EEE Department, Gokaraju Rangaraju Institute of Engineering & Technology, Hyderabad, India

**Abstract.** Multilevel inverters have more prominent features than 2-level inverter due to various advantages like voltage quality, low EMI etc. The semi cross switched multilevel converter topology need less number of semiconductor switches compared to cascaded H-bridge multilevel inverter, and can be implemented to any number of voltage levels. The operating modes of 7-level semi cross switched multi level inverter are discussed. Three phase seven level inverter fed induction motor is implemented in MATLAB/SIMULINK.

## **1** Introduction

Now a day's multilevel inverters grab the attention of researchers due to the various advantages like quality output waveform, low EMI, low THD and are suitable for low and medium voltage industrial applications. Many multi-level inverter topologies are proposed and popular among them are the neutral point clamped [2], [3], flying capacitor [4], and cascaded H-bridge [5] structures, neutral point clamped and Flying capacitor multilevel inverters require complex circuitry with the increase in number of levels.

The main topologies of cascade H bridge is symmetrical with equal voltage sources and asymmetrical with unequal DC sources. The problem with asymmetrical topologies is that some switches have to process through main part of voltage so some high voltage switches are required.

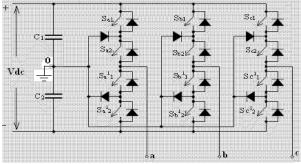

Fig. 1. 3-Phase 3-level Capacitor-Clamped MLI

Fig. 2. 3-Phase 3-level Diode-Clamped MLI

### 2 Cascaded H-bridge Multilevel Inverter

The cascaded H-bridge(CHB) inverters are more interested due to the greater demand of medium-voltage high-power inverters. Full bridge strings are connected in cascaded form with separate dc sources to form CHB. Each full-bridge string generates three voltages at the output  $+V_{dc}$ , 0 and  $-V_{dc}$ .

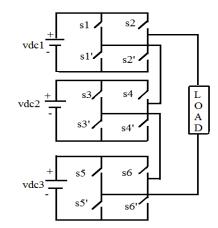

Fig. 3. Single Phase Cascaded H-bridge 7-level Inverter

<sup>\*</sup> Corresponding author: janigasrinivasrao@gmail.com

<sup>©</sup> The Authors, published by EDP Sciences. This is an open access article distributed under the terms of the Creative Commons Attribution License 4.0 (http://creativecommons.org/licenses/by/4.0/).

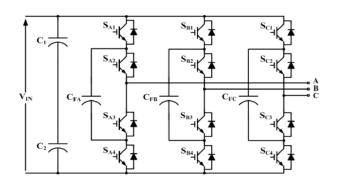

Fig. 4. 3-Phase 3-level Diode-Clamped MLI

| I able1: Switching table for /-level CHB MLI |                           |                   |  |  |

|----------------------------------------------|---------------------------|-------------------|--|--|

| MODE                                         | Switches ON               | O/P<br>Voltage    |  |  |

| 1                                            | $S_1 S_2 S_3 S_4 S_5 S_6$ | V <sub>de</sub>   |  |  |

| 2                                            | $S_1 S_2 S_3 S_4 S_5 S_6$ | 2V <sub>de</sub>  |  |  |

| 3                                            | $S_1 S_2 S_3 S_4 S_5 S_6$ | 3V <sub>de</sub>  |  |  |

| 4                                            | $S_1 S_2 S_3 S_4 S_5 S_6$ | 0V <sub>de</sub>  |  |  |

| 5                                            | $S_1 S_2 S_3 S_4 S_5 S_6$ | -V <sub>de</sub>  |  |  |

| 6                                            | $S_1 S_2 S_3 S_4 S_5 S_6$ | -2V <sub>de</sub> |  |  |

| 7                                            | $S_1 S_2 S_3 S_4 S_5 S_6$ | -3V <sub>de</sub> |  |  |

Table1: Switching table for 7-level CHB MLI

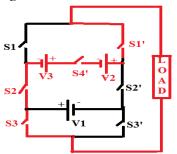

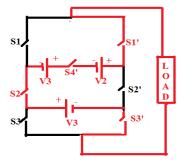

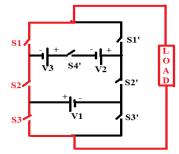

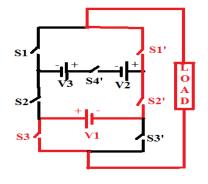

# SEMI CROSS SWITCHED MULTI LEVEL INVERTER

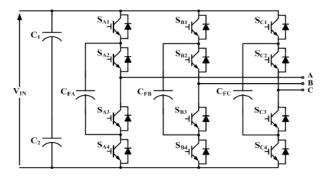

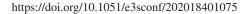

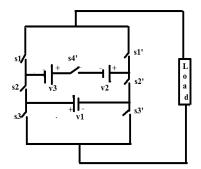

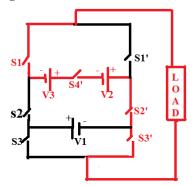

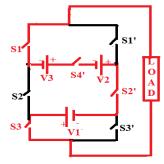

In this topology the switches are connected as shown in figure5 and this topology requires less number of switches compared to CHB. For 7-level inverter the number of switches required is only seven i.e S1, S2, S3,S1', S2', S3', S4' Therefore, the complexity in driver circuit, number of switches required, number of switches conducting, THD and efficiency [1] reduces. So size and cost of the inverter is reduced compared to CHB multilevel inverter.

DC Voltage sources V1(100v), V2(100v), V3(100v) for one phase are connected as shown fig. 5. The switches switched as per requirement of voltage level.

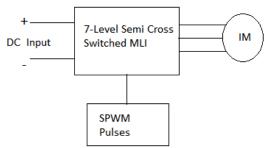

**Fig.5**. Block Diagram of 7-level semicross switched MLI fed induction motor drive

Fig.5. Single phase semi-cross switched multi level inverter

## 2.1 Modes of Operation

The switching operation of 7-level semi cross switched multilevel inverter shown below

Mode-1:

- > The switches s1, s2 and s3' are in ON state.

- > The voltage across this load is +vdc.

Mode-2:

- > The switches s1, s2', s3' and s4' are in ON state.

- $\succ$  The voltage across the load is +2vdc.

Mode-3:

- > The switches  $s_2$ ,  $s_1$ ', $s_3$ ' and  $s_4$ ' are in ON state.

- > The voltage across the load is +3vdc.

#### Mode-4:

- > The switches s1, s2, and s3 are in ON state.

- The voltage across this load is 0.

#### Mode-5:

- The switches s3,s1' and s2' are in ON state.

- ➤ The voltage across this load is -vdc.

Mode-6:

- > The switches s2, s3, s1'and s4'are in ON state.

- $\blacktriangleright$  The voltage across this load is -2vdc.

Mode-7:

- > The switches s1, s3, s2'and s4' are in ON state.

- The voltage across this load is -3Vdc.

### 3. Results

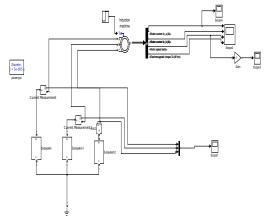

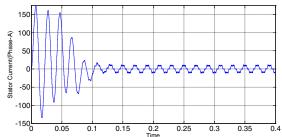

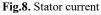

Simulation of three phase 7-level cascaded H bridge multilevel inverter and semi cross switched multilevel inverter induction motor is performed using MATLAB/SIMULINK environment.

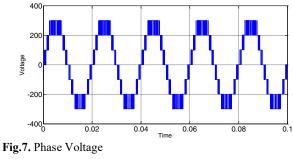

## 3.1 Three phase 7-level cascaded H-bridge multilevel inverter fed IM

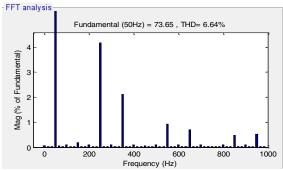

Fig.9. THD analysis of voltage

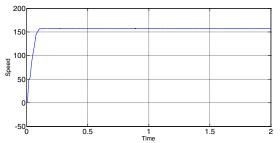

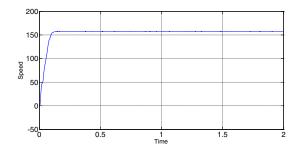

Fig.10. Speed of induction motor

3.2 Three phase 7-Level semi cross switched multilevel inverter

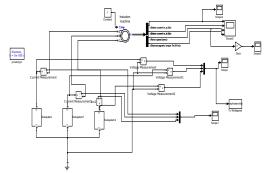

**Fig.11.** simulink diagram of three phase 7-level semi-cross switched multilevel inverter fed IM

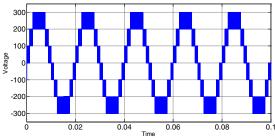

Fig.12. Phase voltage

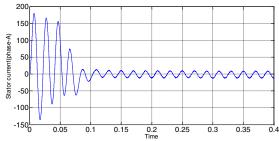

Fig.13. Stator current

Fig.14. THD analysis of voltage

Fig.15. Speed of induction motor

| Table 2. Comparison table for number of switching devices |                              |          |                            |         |  |  |

|-----------------------------------------------------------|------------------------------|----------|----------------------------|---------|--|--|

| OUTPUT<br>VOLTAG<br>E<br>LEVELS                           | NUMBER OF SWITCHING DEVICES  |          |                            |         |  |  |

|                                                           | Cascaded H-Bridge<br>MLI     |          | semi-cross switched<br>MLI |         |  |  |

|                                                           | 1-Phase                      | 3-Phase  | 1-Phase                    | 3-Phase |  |  |

| 7<br>LEVEL                                                | 12                           | 36       | 7                          | 21      |  |  |

| Table 3. Comparison table for THD                         |                              |          |                            |         |  |  |

| OUTPUT                                                    | THD                          |          |                            |         |  |  |

| VOLTAG                                                    | Cascaded H-Bridge semi-cross |          |                            |         |  |  |

| E<br>LEVELS                                               | MLI                          |          | switched MLI               |         |  |  |

| LEVELS                                                    |                              |          |                            |         |  |  |

| 7<br>LEVEL                                                | 6.68                         |          | 6.64                       |         |  |  |

| Table 4. Comparison table for losses                      |                              |          |                            |         |  |  |

| OUTPUT _                                                  | Losses/Phase(w)              |          |                            |         |  |  |

| VOLTAG                                                    | Cascaded H                   | I-Bridge | semi-cross switched        |         |  |  |

| E                                                         | ML                           | Ι        | MLI                        |         |  |  |

| LEVELS -                                                  |                              |          |                            |         |  |  |

| 7<br>LEVEL                                                | 7.34                         | 4        | 4.28                       |         |  |  |

## 4. Conclusions

The three phase 7- level cascaded H-bridge multilevel inverter and three phase 7-level semi cross switched multilevel inverter fed IM is simulated. From the analysis it clear that number of switches required, THD, and losses are also reduced for semicross switched multilevel inverter.

## Acknowledgement:

Authors would like to thank All India Council for Technical Education (AICTE), Govt. of INDIA for sanction of grants under Reserach Promotion Scheme (RPS). *Grant Number:* 8-174/RIFD/RPS(Policy-1)/2018-19 dt: 22 Nov 2019.

## **References:**

1. *E.Avinash, L.Jebaraj* "A New Variable Frequency Inverted Sine Carrier PWM Modulated Semi-Cross Switched Multilevel Inverter Topologies" 2016 International Conference on Circuit, Power and Computing Technologies [ICCPCT]

- 2. M. Fracchia, T. Ghiara, M. Marchesoni, and M. Mazzucchelli, "Optimized modulation techniques or the generalized N-level converter," *in proc. IEEE power electronics specialist Conf*, 1205-1213, *Madrid*, Spain, 1992.

- 3. K. A. Corzine and J. R. Baker, "Reduced partscount multilevel retifiers," "*IEEE Trans. Ind. Electron.*" vol.49, no.3, pp. 766-774, Aug 2002.

- 4. Srinivas Rao J., Srinivasa Varma, P., Suresh Kumar. T, International Journal of Power Electronics and Drive Systems, 9(3), pp. 1202-1213, 2018

- 5. F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing," "*IEEE Trans. Ind. Applica*," vol. 37, pp. 611-618, Mar./April 2004.

- 6. Suresh Kumar Tummala, Dhasharatha G, *E3S Web* of Conferences 87, 01030 (2019)

- Tummala Suresh Kumar, Kosaraju Satyanarayana, Materials Today: Proceeding, 26 (2), 3228-3233, (2020).

- 8. Rajagiri A, MN Sandhya, Nawaz S, Suresh Kumar T, *E3S Web of Conferences* 87 01004 (2019)

- 9. Suresh Kumar T, Sankar V, 2011 IEEE India Conference, INDICON, 2011

- Bankupalli, P.T., Srikanth Babu, V., Suresh Kumar. T, International Journal of Applied Engineering Research, 10(16), pp. 37057-37062, 2015.

- 11. Yogeswara Reddy B, Srinivas Rao J, Suresh Kumar T, Nagarjuna A, International Journal of Innovative Technology and Exploring Engineering, 8(11), 1194-1198, 2019.

- 12. Srinivasa Rao D, Sandhya Rani MN, Sarfaraz Naw az Syed and Suresh Kumar Tummala, *E3S Web of Conferences* 87 01003 (2019)