# Comparative Exploration of 19-level and 21-level Cascaded H- Bridge MLI with Cross H-Bridge MLI

Srinivas Rao J<sup>1\*</sup>, Tummala Suresh Kumar<sup>2</sup>, Hassan Mohmmed Al-Jawahry<sup>3</sup>, Manisha Saini<sup>4</sup>

Abstract. Present days renewable energy sources based grids are developing which needs inverters to convert power from DC to AC. 2-level inverters were used for this purpose to overcome the drawbacks of 2-level inverters multilevel inverters are developed. Because of the combination of numerous devices in a series structure, multilevel inverters provide outstanding solutions to high voltage, high power applications. With the use of suitable simulations and mathematical analysis, this paper compares the performance of 19 and 21-level cascaded H-Bridges with cross H-Bridge MLI. Total Harmonic Distortion levels, switching device count, and inverter output voltage and current are all compared. The primary issues brought up in this study are limitations of a number of switching devices that can support high voltage in the inverter. The benefit of this research is that it identifies the right inverter that can be utilised for real-time applications by taking the variables into account. The count of switching devices, output voltage, current, and harmonic distortion, among other factors. The Matlab/Simulink Platform is used to validate the analysis.

#### 1 Introduction

Conversion of power from DC to AC is one of the essential parts of the electrical power system. Initially 2-level inverters were employed for this purpose, but the major issues with 2-level inverters are low quality ouput voltage, high stress across the switches and large filter requirement. To mitigate these issues multilevel inverters(MLI) are invented. The primary premise of MLI is to spread the inverter's working voltage among switches in the circuit, which decreases voltage stress across the switches and allows low rating switches to be utilised in high voltage/power rating applications. As the level of output voltage rises, the level of harmonics falls at low switching frequencies, lowering the cost of filters. [1-2].

The diode clamped (NPC) MLI, capacitor clamped (FC) MLI, and cascaded H-Bridge (CHB) MLI are the conventional MLI topologies [3-5]. The key drawbacks of these

<sup>&</sup>lt;sup>1</sup>AssociateProfessor, EEE Department, Anurag Engineering College, Kodad, TS, India-508206

<sup>&</sup>lt;sup>2</sup> EEE Department, Gokaraju Rangaraju Institute of Engineering and Technology, Hyderabad, INDIA

<sup>&</sup>lt;sup>3</sup>The Islamic University, Faculty of Engineering, Najaf, Iraq

<sup>&</sup>lt;sup>4</sup> Uttaranchal School of Computing Sciences, Uttaranchal University, Dehradun 248007 INDIA

<sup>\*</sup> Corresponding author: janigasrinivasrao@gmail.com

traditional MLI topologies include an increase in the quantity of switches and auxiliary components, which increases the dimension and price of the inverter [6-8]. The capacitor voltage in the NPC and FC MLI topologies may be managed using redundant switching states, but as the voltage level grows, the quantity of capacitors and requirement of clamping diodes increases, as does the complexity of the control method.

The H-Bridge cells with DC sources are linked in series in a cascaded H-Bridge MLI. The CHB MLI is classed as symmetrical [9-11] or asymmetrical [12-14] based on the kind of DC sources. The symmetric topology provides high modularity and packing due to the same construction of each H - Bridge, but the number of switches grows fast as the output voltage level increases. With an asymmetric architecture, the output voltage may be raised with fewer switches, but the rating of some of the switches is almost equal to the maximum working voltage, making hardware circuit design more difficult. In recent years, several new topologies have been developed. MLI are gaining popularity due to their numerous uses. Multilevel output from a multi winding transformer [15-16] is not cost effective for high power/voltage applications.

This paper discusses about comparison exploration of sinusoidal PWM controlled 19-level and 21-level cross H-Bridge (CRHB) and CHB MLI topologies in terms of %THD, number of switches, voltage across the switches and total voltage stress of the inverter. The simulation is performed with MATLAB/SIMULINK.

# 2 Mathematical analysis

#### 2.1 Cross H-Bridge

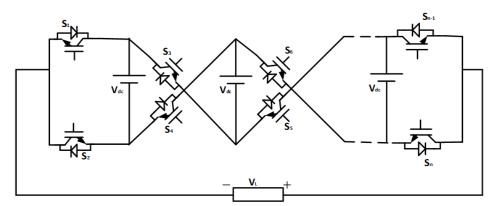

Fig. 1. Circuit representation of N-level single cross H-Bridge MLI

The CRHB MLI [17] is connected with particular cross connections with distinct DC sources as shown in fig.1.

The association between the output voltage level, the quantity of switches, and the quantity of voltage sources:

$$N_s = V_L + 1$$

(1)

$V_L = 2*V_S + 1$  (2)

$N_s = 2(V_S + 1)$  (3)

$N_D = \frac{V_L + 1}{2}$  (4)

### 2.2 Cascaded H-Bridge

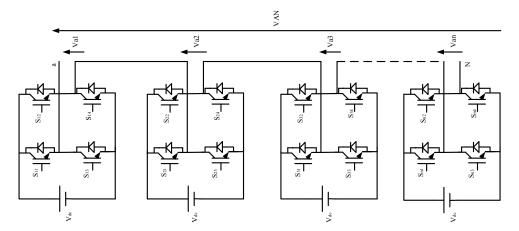

In CHB MLI, the H-Bridge cells with DC source are linked in series. Each H-Bridge consists of four controlled switches. The circuit configuration of CHB-MLI is represented in fig.2.

Fig. 2. Circuit representation of N-level single cascaded H-Bridge MLI

$$N_s = 2*(V_L - 1)$$

(5)

$V_L = 2*V_S + 1$  (6)

$N_S = 4*V_S$  (7)

$N_D = V_L - 1$  (8)

where

$V_L$  is output voltage level,

$N_s$  is quantity of switches,

$V_s$  is quantity of voltage sources,

$N_D$ =no. of switching devices in current path.

# Switches Voltage rating:

In CRHB MLI the voltage stress across switches S<sub>1</sub>, S<sub>2</sub>, S<sub>n-1</sub> and S<sub>n</sub> is V<sub>dc</sub> and other switches voltage stress is  $2V_{dc}$  and the voltage stress of all switches in CHB MLI is  $V_{dc}$  [18-20]. The total voltage stress of CHB MLI and CRHB MLI is =  $2*(V_L - 1)*V_{dc}$ where  $V_L$  is level of output voltage.

#### 2.3 Switch losses

The dominant losses of the power electronic switches are conduction and switching losses [21-23]. Conduction losses are due to conduction of switches. Switching losses are due to turn on and turn off of switches.

The transistor average conduction losses  $(P_c, T(t))$  and diode  $(P_c, D(t))$  can be represented as follows:

$$P_{c}, T = \frac{1}{2\pi} \int [V_{T} + R_{T}i^{\beta}(t)] i(t)d(\omega t)$$

$$P_{c}, D = \frac{1}{2\pi} \int [V_{D} + R_{D}i(t)]i(t) d(\omega t)$$

(9)

(10)

$$P_{c}, D = \frac{1}{2\pi} \int [V_{D} + R_{D}i(t)]i(t) d(\omega t)$$

(10)

The per cycle conduction total conduction losses of MLI

$$P_c = (P_c, T + P_c, D) * N_D$$

(11)

The switching losses is given as

$$P(sw) = f * (T_{on} * E_{on} + T_{off} * T_{off} * E_{off})$$

(12)

Where  $V_T$  and  $V_D$  are transistor and diode voltage drop respectively.

$R_T$  and  $R_D$  are equivalent resistance of transistor and diode

f= frequency,

$T_{on}$  = number of times the switch is turned on,

$T_{off}$  = number of times the switch is turned off.

#### 3 Results and Discussion

The simulation of 19-level and 21-level cross H-Bridge and cascaded H-Bridge MLI is done in MATLAB/SIMULINK environment. The RL load is considered with R=10 $\Omega$  and L-100mH. Results of voltage, current, and %THD are presented and compared.

#### 3.1 19-level cascaded H-Bridge MLI

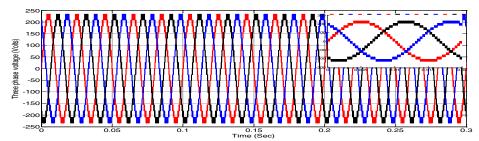

Fig. 3. Three phase voltage

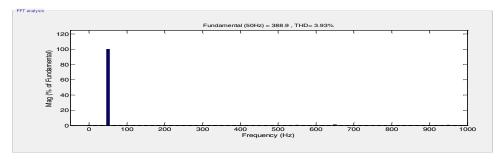

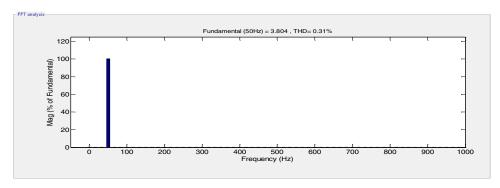

Fig. 4. %THD of voltage

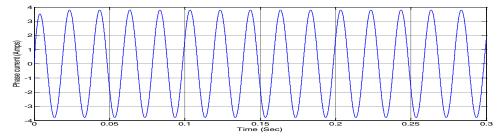

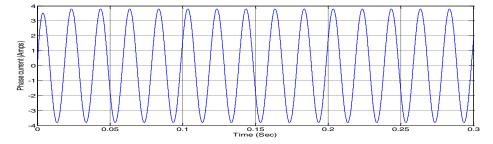

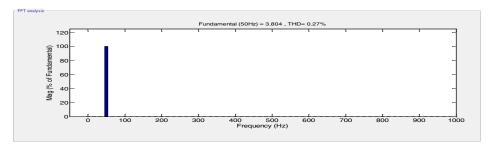

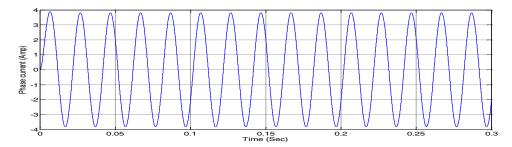

Fig. 5. Phase current

Fig. 6. %THD of current

Fig.3. represents three phase 19-level output voltage with 230V peak to peak, Fig.4. represents %THD of voltage which is recorded as 3.93, Fig.5. represents phase current with 3.8A peak to peak and Fig.6. represents %THD of current which is recorded as 0.31.

# 3.2 19-level cross H-Bridge MLI

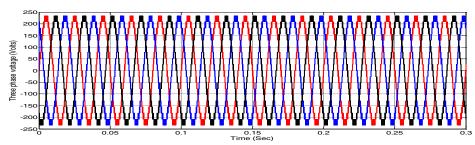

Fig. 7. Three phase voltage

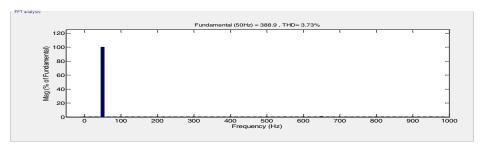

Fig. 8. %THD of voltage

Fig. 9. Phase current

Fig. 10. %THD of current

Fig.7. represents three phase 19-level output voltage with 230V peak to peak, Fig.8. represents %THD of voltage which is recorded as 3.73, Fig.9. represents phase current with 3.8A peak to peak and Fig.10. represents %THD of current which is recorded as 0.27.

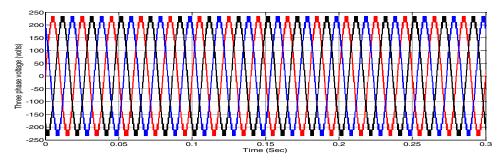

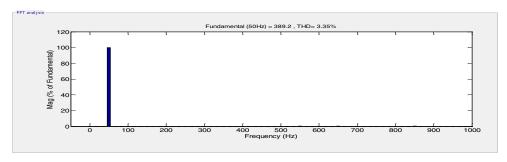

## 3.3 21-level cascaded H-Bridge MLI

Fig. 11. Three phase voltage

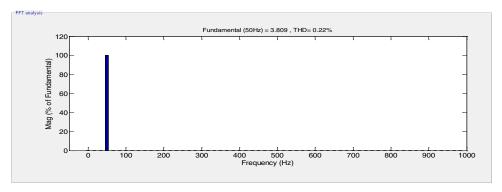

Fig. 12. %THD of voltage

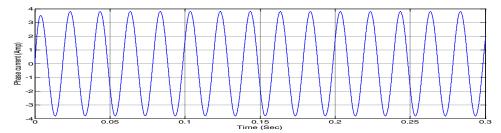

Fig. 13. Phase current

Fig. 14. %THD of current

Fig.11. represents three phase 21-level output voltage with 230V peak to peak, Fig.12. represents %THD of voltage which is recorded as 3.35, Fig.13. represents phase current with 3.8A peak to peak and Fig.14. represents %THD of current which is recorded as 0.22.

# 3.4 21-level cross H-Bridge MLI

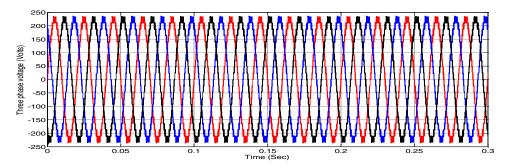

Fig. 15. Three phase voltage

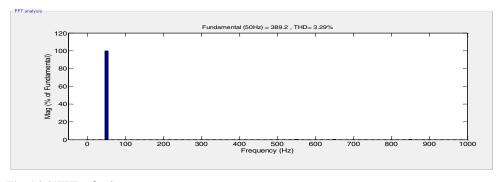

Fig. 16. %THD of voltage

Fig. 17. Phase current

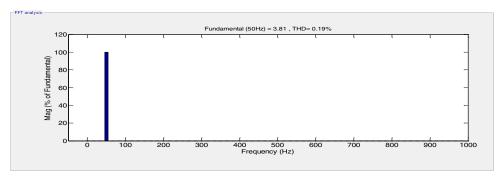

Fig. 18. %THD of current

Fig.15. represents three phase 21-level output voltage with 230V peak to peak, Fig.16. represents %THD of voltage which is recorded as 3.29, Fig.17. represents phase current with 3.8A peak to peak and Fig.18. represents %THD of current which is recorded as 0.19.

Table 1. represents the comparative analysis of number of switches for 19 and 21-level CHB and CRHB MLI topologies. From the table it is clear that number of switches required for CRHB MLI topology is reduced by 50 percent.

| O/P VOLTAGE LEVELS | CHB MLI |     | CRHB MLI |     |

|--------------------|---------|-----|----------|-----|

|                    | 1-Ф     | 3-Ф | 1-Ф      | 3-Ф |

| 19-level           | 40      | 120 | 20       | 60  |

| 21-level           | 44      | 132 | 22       | 66  |

Table 1. Number of switching devices Vs O/P voltage levels

Table 2. represents the comparative analysis of switch losses for 19 and 21-level CHB and CRHB MLI topologies. From the table it is clear that the losses with CRHB MLI topology are reduced by 24.19 percent with 19-level output and 24.9 percent with 21-level output. Table 3. represents the comparative analysis of %THD for 19 and 21-level CHB and CRHB MLI topologies. From the table it is clear that the %THD of voltage with CRHB MLI topology are reduced by 3.5 percent with 19-level output and 1.7 percent with 21-level output and the %THD of current with CRHB MLI topology are reduced by 12.9 percent with 19-level output and 13.6 percent with 21-level output.

| . ,                |         |       |          | C     |

|--------------------|---------|-------|----------|-------|

| O/P VOLTAGE LEVELS | CHB MLI |       | CRHB MLI |       |

|                    | 1-Ф     | 3-Ф   | 1-Ф      | 3-Ф   |

| 19-level           | 21.41   | 64.23 | 16.23    | 48.69 |

| 21-level           | 23.32   | 69.96 | 17.51    | 52.53 |

**Table 2.** Total losses(w) of switches Vs O/P voltage levels

Table 3. %THD Vs O/P voltage levels

| O/P VOLTAGE LEVELS | CHB MLI |         | CRHB MLI |         |

|--------------------|---------|---------|----------|---------|

|                    | Voltage | Current | Voltage  | Current |

| 19-level           | 3.93    | 0.31    | 3.73     | 0.27    |

| 21-level           | 3.35    | 0.22    | 3.29     | 0.19    |

#### 4 Conclusion

Multilevel inverters are one of the essential parts of power systems to convert power from DC to AC. This paper discussed about comparative exploration of 19-level and 21-level CHB and CRHB MLI topologies. The comparison is done in terms of number of switches, %THD and total switch losses of inverter. From the results it is clear that the performance of CRHB topology is better in terms of number of switches, %THD and total switch losses of inverter compared to cascaded H-Bridge MLI topology.

#### References:

- P. R. Bana, K. P. Panda, R. T. Naayagi, P. Siano and G. Panda, "Recently Developed Reduced Switch Multilevel Inverter for Renewable Energy Integration and Drives Application: Topologies, Comprehensive Analysis and Comparative Evaluation," in *IEEE Access*, vol. 7, pp. 54888-54909, 2019.

- 2. K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu and S. Jain, "Multilevel Inverter Topologies with Reduced Device Count: A Review," in *IEEE Transactions on Power Electronics*, vol. 31, no. 1, pp. 135-151, Jan. 2016.

- 3. J. Rodriguez, S. Bernet, P. Steimer, and I. Lizama, "A survey on neutral point clamped inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2219–2230, Jul. 2010.

- M. M. Shobini, J. Kamala and R. Rathna, "Analysis and simulation of flying capacitor multilevel inverter using PDPWM strategy," 2017 International Conference on Innovative Mechanisms for Industry Applications (ICIMIA), Bangalore, 2017.

- 5. M. Pamujula, A. Ohja, R. D. Kulkarni and P. Swarnkar, "Cascaded 'H' Bridge based Multilevel Inverter Topologies: A Review," 2020 International Conference for Emerging Technology (INCET), Belgaum, India, 2020.

- P. R. Bana, K. P. Panda, R. T. Naayagi, P. Siano and G. Panda, "Recently Developed Reduced Switch Multilevel Inverter for Renewable Energy Integration and Drives Application: Topologies, Comprehensive Analysis and Comparative Evaluation," in *IEEE Access*, vol. 7, pp. 54888-54909, 2019.

- 7. G.T. Kim and T. A. Lipo, "VSI-PWM rectifier/inverter system with a reduced switch count," *IEEE Tran. Ind. Appl.*, vol.32, no.6, pp.1331–1337, Nov./ Dec. 1996.

- 8. V. V. Nagi Reddy, D. V. A. Kumar, and V. R. Kota, "A multilevel UPQC for voltage and current quality improvement in distribution system," *Int. J. Power Electron. Drive Syst.*, vol. 10, no. 4, p. 1932, 2019,v10.i4.pp1932-1943.

- 9. S. S. Lee, M. Sidorov, N. R. N. Idris and Y. E. Heng, "A Symmetrical Cascaded Compact-Module Multilevel Inverter (CCM-MLI) With Pulsewidth Modulation," in IEEE Transactions on Industrial Electronics, vol. 65, no. 6, pp. 4631-4639, June 2018.

- L. Nanda, P. Bharti and A. Dasgupta, "Symmetrical And Asymmetrical Topology of Cascaded Multilevel Inverter With Reduced Number of Switches And DC Sources," 2019 IEEE International Conference on Sustainable Energy Technologies and Systems (ICSETS), Bhubaneswar, India, 2019, pp. 230-235.

- 11. M. H. Yatim, A. Ponniran, M. A. Zaini, M. S. Shaili, N. A. S. Ngamidun, and A. N. Kasiran, "Symmetrical and Asymmetrical Multilevel Inverter Structures with Reduced Number of Switching Devices," vol. 11, no. 1, pp. 144–151, 2018, ijeecs.v11.i1.pp144-151.

- 12. K. Thakre, K. B. Mohanty, V. Kommukuri and R. N. Mishra, "Symmetrical and asymmetrical multilevel inverter using less number of switches," TENCON 2017 2017 IEEE Region 10 Conference, Penang, 2017, pp. 1032-1036.

- 13. B. Mahato, S. Mittal and P. k. Nayak, "Generalized Symmetrical/Asymmetrical Single-phase MLI Topology," 2018 International Conference on Recent Trends in Electrical, Control and Communication (RTECC), Malaysia, Malaysia, 2018, pp. 182-187.

- D. A. B. Zambra, C. Rech and J. R. Pinheiro, "Comparison of Neutral-Point-Clamped, Symmetrical, and Hybrid Asymmetrical Multilevel Inverters," in IEEE Transactions on Industrial Electronics, vol. 57, no. 7, pp. 2297-2306, July 2010.

- Rao, J.S., Tummala, S.K. & Kathuri, N.R., "Comparative analysis of PWM techniques for 15level cross-connected H bridge inverter," Nanotechnology for environmental engineering, Vol. 7, PP: 393-403, 2022.

- 16. D. A. B. Zambra, C. Rech, and J. R. Pinheiro, "A comparative analysis between the symmetric and the hybrid asymmetric nine-level series connected H-bridge cells inverter," in *Proc. Eur. Conf. Power Electron. Appl.*,2007, pp. 1–10.

- 17. Mohammad Farhadi Kangarlu, Ebrahim Babaei "Cross-switched multilevel inverter: an innovative topology" IET Power Electron., 2013, Vol. 6, Iss. 4, pp. 642–651.

- 18. Rao, J.S, P.S. Varma, S. K. Tummala, "Novel Switching Design Structure for Three Phase 21-Level Multilevel Inverter Fed BLDC Drive Application", International Journal of Power Electronics and Drive System, Vol. 9, No. 3, Sept 2018, pp. 1202~1213, ISSN: 2088-8694.

- A. Anan, T. K. Chakraborty, and K. Sultan Mahmood, "A Single-Phase Cascaded H-Bridge Multilevel Inverter with Reduced Switching Devices and Harmonics," 2018 6th IEEE Int. Conf. Smart Energy Grid Eng. SEGE 2018, pp. 222–225, 2018.

- J. S. Rao, S. K. Tummala, and N. R. Kuthuri, "Comparative investigation of 15 level and 17 level cascaded h-bridge mli with cross h-bridge mli fed permanent magnet synchronous motor," *Indones. J. Electr. Eng. Comput. Sci.*, vol. 21, no. 2, pp. 723–734, 2020.

- 21. B. Alamri and M. Darwish, "Power loss investigation in HVDC for cascaded H-bridge multilevel inverters (CHB-MLI)," 2015 IEEE Eindhoven PowerTech, PowerTech 2015, vol. 2, no. 6, pp. 230–238, 2015.

- 22. B. Alamri and M. Darwish, "Precise modelling of switching and conduction losses in cascaded h-bridge multilevel inverters," *Proc. Univ. Power Eng. Conf.*, 2014.

- 23. Z. Boussada, O. Elbeji and M. Benhamed, "Different topologies and control techniques of multi level inverter: A literature survey," 2017 International Conference on Green Energy Conversion Systems (GECS), Hammamet, 2017, pp. 1-5.